采用XDMA是许多人常用xilinx库实现NVMe或其他传输的方法。但是,XDMA介绍较少,在高速存储设计时,尤其是PCIe4.0模式下,较难发挥其最优性能,因此,直接采用PCIe实现NVMe功能。

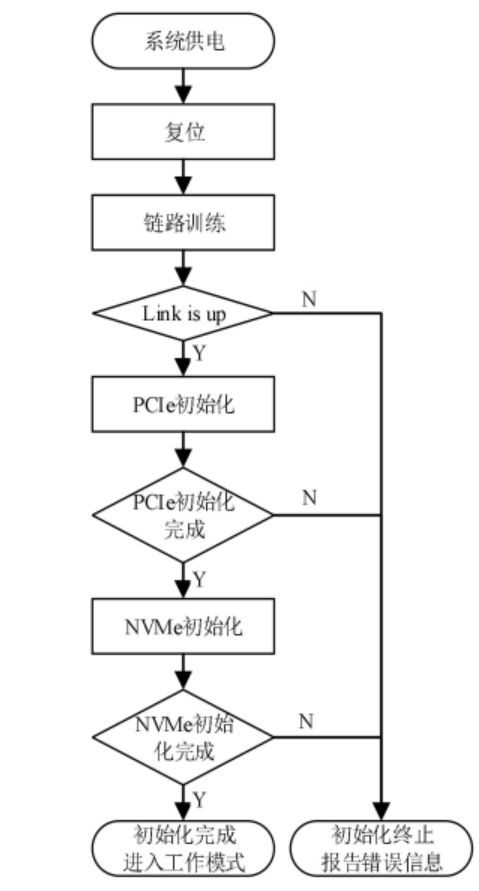

这里主要分享基于PCIe3.0接口的NVMe IP设计简介。有需要更高性能需求的,请先了解其性能简介,在文末给出链接。它的系统初始化流程主要分为链路训练、PCIe 初始化和 NVMe 初始化, 分别实现 PCIe链路连接、 PCIe 设备枚举配置和 NVMe 设备配置功能。 其中链路训练由 PCIE 集成块实现, 初始化模块根据链路训练完成信号和初始化启动信号来执行 PCIe 初始化和NVMe 初始化。

图1 系统初始化流程

系统初始化的主要流程如图 1 所示, 在系统供电后, 首先进入复位状态, 一旦退出复位状态, 由 PCIE 集成块执行链路训练, PCIE 集成块提供了 LinkUp 信号用于指示链路训练是否成功。 链路训练消耗时间为毫秒级别, 为了确保系统的稳定, 在系统复位退出后 1 秒时如果 LinkUp 信号仍为低电平, 则断言为链路训练失败, 初始化流程终止。

如果 LinkUp 为高电平, 此时用户可通过系统控制模块启动 PCIe 初始化,进入 PCIe 初始化状态。 PCIe 初始化状态机在执行完初始化流程后, 会报告初始化执行状态, 如果在初始化过程中出错, 进入初始化终止状态并将错误信息反馈到初始化状态寄存器。 当 PCIe 初始化正常完成后, 可以进入 NVMe 初始化状态, NVMe 初始化也由用户通过系统控制模块启动。 当 NVMe 初始化正常完成后, 系统的初始化完成, NoP 逻辑加速引擎进入正常工作模式。